Универсальный триггер

JK-триггер

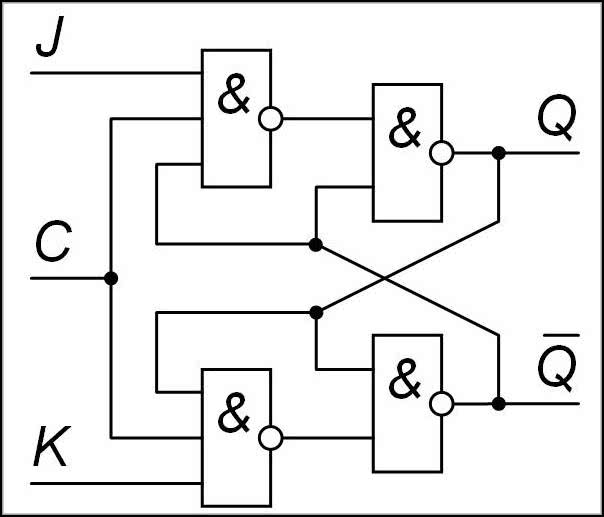

JK-триггером называют автомат Мура с двумя устойчивыми состояниями и двумя входами J и K, который при условии J * K = 1 осуществляет инверсию предыдущего состояния (т.е. при J*K=1, Q(t+1) = Q(t)), а в остальных случаях функционируют в соответствии с таблицей истинности RS триггера, при этом вход J эквивалентен входу S, а вход K — входу R. Этот триггер уже не имеет запрещенной комбинации входных сигналов и его таблица истинности, то есть зависимость Q(t+1) = f имеет вид:

Таблица истинности JK-триггера:

| J | K | Q(t) | Q(t+1) |

По этой таблице можно построить диаграмму Вейча для Q(t+1), которую можно использовать для минимизации, и матрицу переходов:

| KQ(t) |

| J |

Матрица переходов JK-триггера:

| J | K | Q(t) | Q(t+1) |

| b1 | |||

| b2 | |||

| b3 | |||

| b4 |

| ____ | _ | |||

| Q(t+1) = J* | Q(t) | v | K | *Q(t) |

В интегральной схемотехнике применяются только тактируемые (синхронные) JK триггера, которые при C=0 сохраняют свое состояние, а при C=1 работают как асинхронные JK триггера.

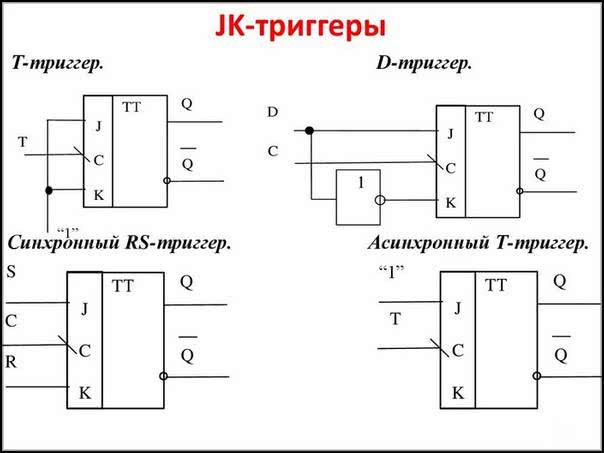

Триггер JK относится к разряду универсальных триггеров, поскольку на его основе путем несложной внешней коммутации можно построить RS-, D— и T— триггера. RS-триггер получается из триггера JK простым наложением ограничения на комбинацию входных сигналов J=K=1, так как эта комбинация является запрещенной для RS триггера.

Счетный триггер на основе JK триггера получается путем объединения входов J и K.

Триггер задержки (D-триггер) строится путем подключения к входу K инвертора, на который подается тот же сигнал, что и на вход J. В этом случае вход J выполняет функцию входа D, а все устройство в целом реализует таблицу переходов D-триггера.

Лекция 6. Структурная схема конечного автомата

В структурной теории автомат представляют в виде композиции двух частей: запоминающей части, состоящей из элементов памяти, и комбинационной части, состоящей из логических элементов:

Комбинационная схема строится на логических элементах, образующих функционально полную систему, а память – на элементарных автоматах, обладающих полной системой переходов и выходов.

Каждое состояние абстрактного автомата ai, где i={0, n}, кодируется в структурных автоматах набором состояний элементов памяти Qi, r={1,R}. Поскольку в качестве элементов памяти используются обычные триггера, то каждое состояние можно закодировать двоичным числом ai = Q1a1Q2a2… Qrar. Здесь аi={0, 1}, a Q – состояние автомата . Отсюда:

| __ | ||

| Qa = | Q | ,еслиa=0 |

| Q | ,еслиa=1 |

Общее число необходимых элементов памяти можно определить из следующего неравенства . Здесь (n+1) – число состояний. Логарифмируя неравенство получим . Здесь ]C [ — означает, что необходимо взять ближайшее целое число, большее или равное C.

В отличии от абстрактного автомата, имеющего один входной и один выходной каналы, на которые поступают сигналы во входном X={x1,x2,…,xm} и выходном Y={y1,y2,…,yk} алфавитах, структурный автомат имеет L входных и Nвыходных каналов. Каждый входной xj и выходной yj сигналы абстрактного автомата могут быть закодированы двоичным набором состояний входных и выходных каналов структурного автомата.

| xi = o1a1 o2a2… oLaL |

| yg = Z1a1Z2a2… ZNaN |

Здесь ofи Zh– состояния входных и выходных каналов соответственно.

Очевидно число каналов L и N можно определить по формулам ; , аналогичным формуле для определения R.

Изменение состояния элементов памяти происходит под действием сигналов U=(U1,U2,…,Ur), поступающих на их входы. Эти сигналы формируются комбинационной схемой II и называются сигналами возбуждения элементарных автоматов. На вход комбинационной схемы II, кроме входного сигнала xj, по цепи обратной связи поступают сигналы Q=(Q1, Q2, …, QR), называемые функцией обратной связи от памяти автомата к комбинационной схеме. Комбинационная схема I служит для формирования выходного сигнала yg, причем в случае автомата Мили на вход этой схемы поступает входной сигнал xj, а в случае автомата Мура – сигнал xj не поступает, так как yg не зависит от xj.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Будет интересно Все о законе Ома: простыми словами с примерами для «чайников»

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

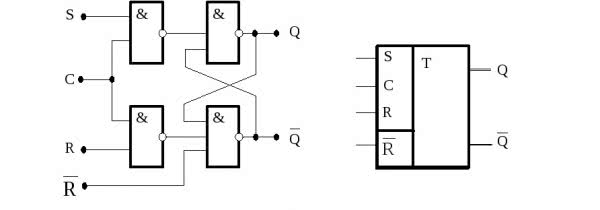

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Асинхронный R-S триггер

Триггеры – это устройства для хранения информации. Они являются костяком более сложных устройств, таких как счетчики, шифраторы, дешифраторы, регистры и прочие устройства.

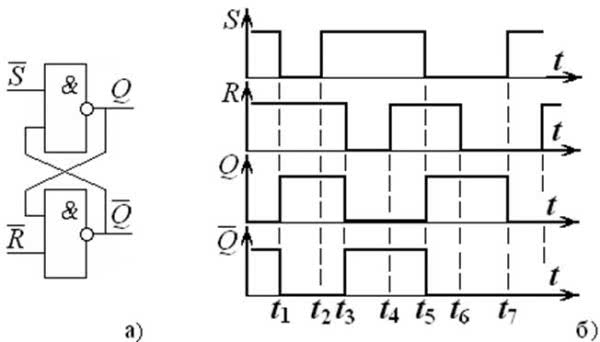

Мы рассмотрим асинхронный R–S триггер на примере двух элементов «И — НЕ». Схема и таблица истинности этого устройства показана ниже:

Как мы можем видеть из схемы, триггер имеет два входа и . На каждый вход подается различная комбинация сигналов (смотри таблицу истинности). Также у триггера есть два выхода – один прямой Q, а один инверсный . Если =0, то Q = 1 и соответственно если =1, то Q = 0.

Схема построена таким образом, что при подаче сигнала S=1 (что равнозначно =0), на выходе получаем Q = 1. S от английского слова set – устанавливать. Когда S=0 (=1),то выход Q = 0. Если мы на вход R подадим сигнал, который будет инверсный по отношению к сигналу S, то при R=1, S=0, единица на выходе Q поменяет свое значение на ноль. Отсюда происходит и название входа, от английского слова reset – сброс, то есть вход R сбрасывает значение, установленное со входа S.

Давайте рассмотрим принцип работы этой схемы. Пускай выходы триггера имели следующие значения Q=0, а = 1.

На вход мы подадим следующие сигналы =0, =1. Поскольку элемент Е1 является инверсным, то на выходе Q будет равным единицы. Элемент Е2 тоже является инверсным и при установлении =1, а также при приходе от выхода Q единицы, на вход элемента «И-НЕ» поступит две единицы, где в итоге получим =0. Соответственно при появлении на входе Е1 =0 и =0 на выходе Q будет установлен сигнал равен единице.

Если мы зеркально изменим сигнал на входе триггера (=1, =0), то на входе Е2 мы получим единицу и ноль, и сигнал на изменится, став равным единице. На входах Е1 появятся две единицы, которые изменят сигнал Q, и он станет равным нулю.

Также если подать на оба входа и подать единицы, то сигналы на выходе не изменятся вообще. Эта комбинация оставляет триггер в предыдущем состоянии (Qn+1=Q).

Рассмотрим случай когда на вход будут поданы следующие сигналы: =0 и =0. Если до этого на выходе Q=0, =1, то на входе Е1 будет единица и ноль, то есть Q изменится на единицу. Тогда на Е2 будет нуль и единица и останется единицей. Соответственно на выходе будет два абсолютно одинаковых сигнала. Такое положение не нормальное для работы триггера, поэтому при его работе комбинации =0 и =0 нужно всячески избегать, так как она является запрещенной. Также если начальные сигналы были Q=1, =0, то подача =0 и =0 приведет к такому же результату, что и в предыдущем случае.

Ниже показан асинхронный R –S триггер на базе элементов «ИЛИ-НЕ», а также его таблица истинности.

Как работает JK-триггер

Это электронное устройство работает строго по определённому алгоритму, предусматривающему поступление входных значений и обеспечивающему формирование выходных.

Как видно из схемы, триггер имеет три входа, на которые поступают следующие сигналы:

- J, K — информационные сигналы. Они принимают значение 0 или 1. Каждой комбинации соответствует определённое выходное значение.

- C — двоичный сигнал, который определяет, будут ли меняться выходные сигналы на основании действующего алгоритма или нет. Обычно срабатывание происходит при переходе от единичного к нулевому значению. Также говорят, что срабатывание происходит при отрицательном фронте сигнала.

В этой схеме имеется два выхода:

- Q — прямой. Выдает значение, которое на данный момент хранится в триггере.

- Q1 также обозначают как Q с горизонтальной чертой сверху — инверсный. Этот сигнал всегда будет противоположным по отношению к Q.

JK-триггер — это своего рода усовершенствованный RS-триггер. В последнем наблюдается одно запрещённое состояние, использование которого приводит к неопределённому результату на выходе. В JK-устройстве такое состояние исключено. В остальном оба элемента действуют аналогично.

JK-триггер — универсальное устройство. На его базе можно построить простой и асинхронный Т-триггер, D-триггер, синхронный RS-триггер

Есть еще комбинированный JK-триггер. От универсального он отличается двумя дополнительными асинхронными входами S и R. Последние позволяют предварительно установить устройство в определенный режим (логического нуля или единицы).

Cинхронные схемы

Бывает, требуется применять схемы с логическими элементами, работающими на основе изменения состояния при создании специальных условий, не зависящих от статуса входов. При этом в схему добавляется логический компонент И, имеющий 2 входа и соединенный с триггерными входами. Теперь входы R и S будут выполняться через терминал И, имеется также третий вход для тактовых импульсов. Изменение работы триггера заключается в том, что на Q̃ и Q состояние будет варьироваться из-за прохождения высокого тактового сигнала на входе, называемого «включить».

Синхронная схема RS триггера

- Когда тактовый сигнал равен 0, выходные значения элементов И идентичны, фиксируя выходные сигналы в последнем запомнившимся статусе;

- При тактовом импульсе, соответствующем единице, вся схема приобретает прозрачность и начинает работать как нормальный РС триггер. При этом оба входа воспринимают сигналы R и S.

Основным преимуществом тактового сигнала является то, что выход этого триггера можно синхронизировать со многими другими схемами и устройствами, которые используют одни и те же тактовые импульсы. Эта компоновка используется для базового расположения памяти, например, применяя различные логические состояния к диапазону из восьми триггеров, а затем посредством синхронного тактового импульса заставляя систему хранить байт данных.

Временные диаграммы

Скважность импульсов

Таблицы истинности иногда не являются лучшим методом описания последовательной схемы. Часто предпочтительнее временная диаграмма синхронизации, которая показывает, как логические состояния в разных точках цепи меняются со временем.

Временная диаграмма RS триггера

На рисунке видно, что в первый момент времени t1 оба сигнала высокие, что вызывает неопределенное состояние. Затем от t1 до t2 S равно 0, R равно 1 на выходе Q устанавливается 1. Еще два неопределенных состояния: от t2 до t3 и от t4 до t5. На промежутке t3-t4 происходит сброс схемы в 0 на выходе Q. А в пределах t6-t7 – недопустимое состояние схемы, когда R и S равны 0.

Значение слова триггер

(англ. trigger), спусковое устройство ( спусковая схема ), которое может сколь угодно долго находиться в одном из двух (реже многих) состояний устойчивого равновесия и скачкообразно переключаться из одного состояния в другое под действием внешнего сигнала. Т. имеет два выхода: основной и инверсный. Каждому состоянию Т. соответствуют определённые сигналы на его выходах, отличающиеся своим уровнем. В одном состоянии на основном выходе Т. формируется сигнал высокого уровня, а на инверсном ≈ низкого; в др. состоянии, наоборот, сигналы высокого и низкого уровней формируются соответственно на инверсном и основном выходах. Т. характеризуется следующими важнейшими параметрами: быстродействием, временем срабатывания, уровнями входных и выходных сигналов. Быстродействие Т. определяется как максимальное возможное число переключений в единицу времени. Время срабатывания определяется временем перехода Т. из одного состояния в другое и характеризует задержку выходного сигнала Т. относительно входного. Под уровнем входного сигнала понимают минимальное значение сигнала, необходимое для переключения Т. Уровень выходного сигнала у большинства Т. не ниже уровня входного сигнала, чем обеспечивается возможность их последовательного соединения без промежуточного усиления.

Наибольшее распространение получили электронные Т., выполненные на электронных лампах, газоразрядных приборах, полупроводниковых диодах, транзисторах разных типов и особенно на интегральных микросхемах; иногда применяются также Т. на магнитных элементах, элементах пневмо- и гидроавтоматики и др. По характеру входных сигналов различают Т. с потенциальными входами (прямым и инверсным) и динамическими входами (также прямым и инверсным). Т. с потенциальными входами реагируют на сигнал высокого уровня на прямом входе и низкого уровня на инверсном входе. Т. с динамическими входами реагируют на перепады (изменения уровня) входных сигналов: положительный на прямом входе и отрицательный на инверсном.

══Наиболее часто применяют: Т. со счётным входом (Т-триггер), который изменяет своё состояние на противоположное с каждым входным сигналом; Т. с двумя установочными входами (R ≈ S-триггер), изменяющий своё состояние только при воздействии управляющего сигнала на определённый вход (R-или S-вход), причём повторное воздействие сигнала на тот же вход Т. не изменяет его состояния; универсальный Т. (J ≈ K-триггер), обладающий свойствами Т-триггера и R ≈ S-триггера; Т. задержки (D-триггер), состояние которого и соответствующий ему выходной сигнал повторяют входной сигнал. Кроме Т. этих типов, применяют комбинированные Т., представляющие собой универсальные многофункциональные устройства с большим числом входов.

Указанные выше Т. относят к симметричным; применяют также несимметричные Т. (Т. Шмитта). Несимметричный Т. переходит из одного состояния в другое по достижении входным сигналом одного уровня (порога срабатывания), а в исходное состояние возвращается при уменьшении входного сигнала до некоторого др. уровня. Существуют и многостабильные Т., обладающие числом устойчивых состояний, большим, чем два.

Т. различных типов применяют в устройствах цифровой вычислительной техники и автоматики. С использованием Т. строятся цифровые автоматы с программным управлением для дискретной обработки информации (в частности, счётчики, пересчётные устройства, регистры разных типов, дешифраторы, сумматоры и др.), формирователи импульсов, цифровые делители частоты и т.д. В цифровой автоматике Т. выполняют функции элементарных автоматов с памятью, имеющих 2 состояния, которым соответствуют два возможных значения двоичной логической переменной (х = 0 и х = 1). Такие Т. подразделяются на асинхронные и синхронные. Синхронные (тактируемые) Т. выполняют свои функции только при воздействии на их входы периодических тактовых сигналов (обычно меандрового типа), синхронизирующих работу Т. Синхронные Т. подразделяются на однотактные и двухтактные. Последние представляют собой систему из двух Т., выполняющих одну и ту же логическую операцию, но со сдвигом во времени на длительность полутакта входного тактового сигнала. Удвоение действий Т. необходимо для разделения во времени приёма информации, доставляемой входными сигналами, и передачи информации с выходов Т. на др. элементы устройства (или на его вход).

Лит.: Ицхоки Я. С., Овчинников Н. И., Импульсные и цифровые устройства, М., 1972; Старостин А. Н., Импульсная техника, М., 1973; Каган Б. М., Каневский М. М., Цифровые вычислительные машины и системы, М., 1973.

Ю. Б. Барабанов, И. А. Данильченко,

Е. И. Петровичев.

Классификация

Если стандартные логические элементы являются строительными блоками комбинационных схем, бистабильные схемы, включая и RS-триггер, являются основными компонентами построения последовательностных логических устройств, таких, как регистры хранения данных, регистры сдвига, устройства памяти или счетчики. В любом случае рассматриваемые триггеры (разумеется, как и все последовательностные схемы) могут быть выполнены в виде следующих основных типов:

1. Асинхронный RS-триггер – схема, которая изменяет состояние сразу при изменении входных сигналов. Для рассматриваемого типа устройств ими являются сигналы на информационных входах R (сброс) и S (установка). Согласно установившейся практике, соответствующие входы называют так же, как и сигналы на них.

2. Синхронный RS-триггер, управляемый статически, работа которого синхронизирована с уровнем определенного тактового сигнала.

3. Триггер по п.2 с динамическим управлением, работа которого синхронизирована с моментами появления фронтов (или спадов) тактового сигнала.

Таким образом, если изменения состояния выходов происходят только при наличии тактового сигнала, который подается на отдельный тактовый вход C, то триггер является синхронным. В противном случае схема считается асинхронной. Чтобы сохранить свое текущее состояние, последовательностные схемы используют обратную связь, т. е. передачу части выходного сигнала на ее вход.

Принцип работы

Логическое устройство будет находиться в устойчивом положении в том случае, если на С=0. В этом случае импульсы, подающиеся на информационный D-вход, никак не влияют на прибор, и выходной импульс определяется записанным ранее значением. Если С=1, то выходной сигнал будет зависеть от того, какой т подан на информационный D-вход. Если D=1, то на выходе будет 1, если D=0, то на выходе будет 0.

RS триггер

Таблица истинности будет иметь вид

| Входной сигнал | Выходной сигнал | Режим работы |

| С | D | Q |

| определяется предыдущим состоянием | Хранение информации | |

| 1 | определяется предыдущим состоянием | |

| 1 | Запись информации | |

| 1 | 1 | 1 |

Внимание! Логический компонент хранит информацию только при подаче нулевого значения на C-вход. Д-триггер выполняется двух типов: с управлением по уровню и с управлением по фронту

Д-триггер выполняется двух типов: с управлением по уровню и с управлением по фронту.

Элементы с управлением по уровню

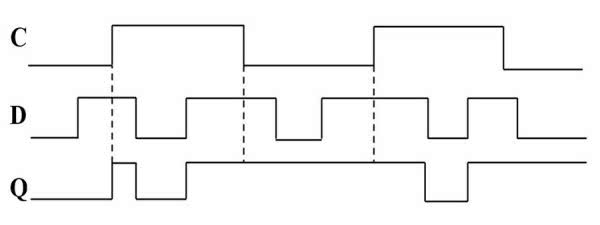

Временная диаграмма работы прибора со статическим управлением (по уровню сигнала) изображена на рисунке ниже.

Временная диаграмма работы d-триггера со статическим управлением

При статическом управлении переход из одного состояния в другое выполняется по уровню. Сигнал с D-входа будет записываться только при высоком уровне на тактовом C-входе.

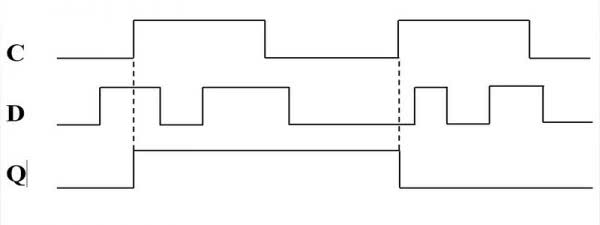

Элементы с управлением по фронту

Данный тип логического устройства срабатывает при переходе с одного уровня на другой. Срабатывание может выполняться в двух случаях: по переднему и заднему фронту. По переднему, если переход выполняется от 0 к 1, и по заднему, если от 1 к 0.

Чтобы переключить d-триггер в нужное нам положение, сначала подаётся 0 или 1 на информационный D-вход. Если необходимо на выходе получить единицу, то D=1, если нужно, чтобы был на выходе ноль, то на D=0.

Затем на С-вход подаётся тактовый импульс. По его изменению элемент переключится в нужное нам состояние. При этом сигнал, который подаётся на D-вход, будет сохранён.

Такая логика работы делает электронный компонент очень удобным для хранения одного разряда двоичного числа (0 или 1). Причём, это состояние д-триггер будет сохранять до тех пор, пока не поступит следующий бит информации.

Временная диаграмма работы d-триггера с динамическим управлением

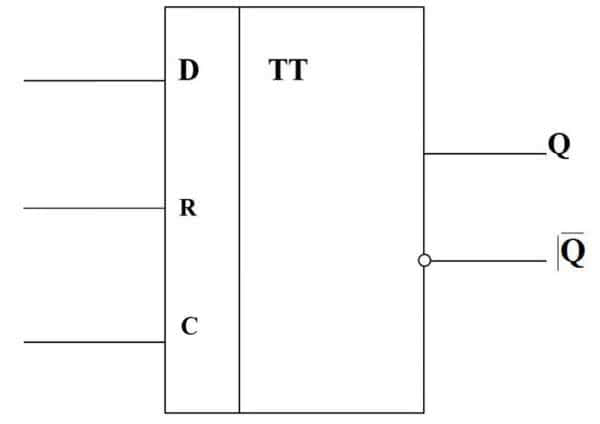

Для сброса д-триггера нужно, чтобы на входах D=0, а С=1. Однако таким образом не всегда можно управлять состоянием, поэтому в схемах используют компоненты с тремя входами.

Схематичное изображение d-триггера с тремя входами

В этом случае добавляется третий R-вход, который отвечает за сброс информации.

Схема реализации d-триггера

В отличие от схем RS, данные устройства управляются с применением одного информационного входа. Это удобно, так как в двоичной системе один бит принимает только два значения (ноль или единицу). Кроме экономии проводников, такое решение помогает изменять задержку с применением регулировок частоты синхронизирующего сигнала.

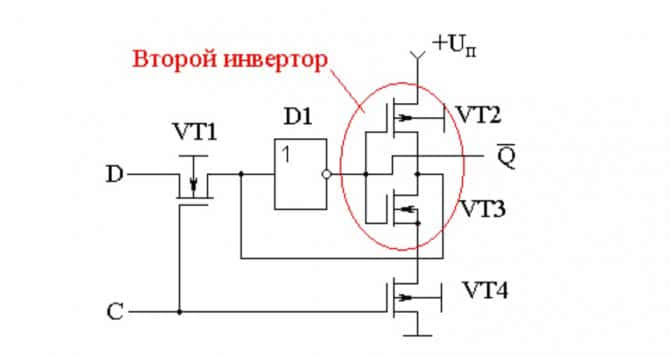

Схема реализации триггера на транзисторах

Вместо рассмотренных выше ТТЛ элементов для создания аналогичного устройства можно применить типовые транзисторы, созданные с применением КМОП технологии. На картинке изображен d триггер, принцип работы которого представлен ниже:

- при отсутствии сигнала на входе C транзистор VT1 находится в закрытом состоянии, не пропускает ток через полупроводниковый затвор;

- в этом состоянии не имеет значения уровень сигнала на D;

- если подать на С единицу, переход откроется;

- инвертор D1 обеспечит передачу на выход Q сигнала;

- два транзистора VT2 и VT3 образуют второй инвертор, который обеспечивает функционирование схемы в режиме типичного D триггера.

Таким образом, как и при работе с элементарными логическими компонентами, здесь данные состояния сохраняются только при нулевом уровне синхронизирующего сигнала. При увеличении его до уровня открытия полупроводникового перехода информация на входе и выходе будет повторяться с минимальной задержкой.

Для объективного анализа схемотехники надо изучить переходные процессы. Дело в том, что базовые для логических уравнений значения (ноль и единица) не всегда способны физически соответствовать идеальным значениям. Допустим, что управляющий сигнал поступает одновременно со сменой информационного. В этом случае триггер переходит в нестабильное состояние.

Ошибки проявляются в сбоях, когда последующие логические элементы ошибочно воспринимают амплитуду входных сигналов. Подобные ошибки могут блокировать полностью работу вычислительных устройств и другой техники.

Паразитные импульсные помехи образуют шумы в радиочастотном диапазоне. Состояние неопределенности увеличивает временные задержки при прохождении сигналов. Чтобы минимизировать вредное влияние и правильно делать конструкторские расчеты, производители триггеров указывают в сопроводительной документации минимальные допустимые параметры:

- setup time – промежуток перед синхронизирующим импульсом;

- hold time – длительность информационного сигнала.

Оценочный параметр MTBF показывает величину, обратно пропорциональную скорости отказов. Им определяют способность триггеров поддерживать стабильность рабочих процессов.