Содержание

Триггеры: Методическое пособие по курсу «Цифровая техника и микропроцессоры», страница 3

R = 0 R = 1

Значит, состояние входа R для рассматриваемого перехода безразлично. Отразим это в первой строчке таблицы возбуждения прочерком в столбце R:

| Q(t) | S | R | Q(t+1) |

| — |

Переходам 0 -> 1 и 1 -> 0 соответствуют однозначные комбинации, а переходу 1 -> 1 — опять две, из которых вытекает безразличность состояния входа S. Заполнив все строки таблицы, получим окончательно таблицу возбуждения RS – триггера:

| Q(t) | S | R | Q(t+1) |

| — | |||

| 1 | 1 | ||

| 1 | 1 | ||

| 1 | — | 1 |

Эта таблица пригодится при синтезе триггеров других типов, а также цифровых автоматов.

1.2. Асинхронный JK – триггер

Нарушим общепринятую последовательность рассмотрения триггеров различных типов и рассмотрим синтез асинхронного JK-триггера, поскольку он является “старшим братом” RS-триггера ввиду большого сходства их таблиц истинности. Таблица истинности JK-триггера почти полностью совпадает с таблицей истинности RS-триггера и отличается лишь тем, что при подаче на входы комбинации «11» JK-триггер обязан переключиться в противоположное состояние.

Вот его таблица истинности (сравните с таблицей истинности RS-триггера):

Табл. 2.Таблица истинностиJK-триггера

| Q(t) | J | K | Q(t+1) | Действие |

| хранение | ||||

| 1 | сброс в 0 | |||

| 1 | 1 | установка в 1 | ||

| 1 | 1 | 1 | инверсия выхода | |

| 1 | 1 | хранение | ||

| 1 | 1 | сброс в 0 | ||

| 1 | 1 | 1 | установка в 1 | |

| 1 | 1 | 1 | инверсия выхода |

Разумно предположить, что JK-триггер может успешно заменять RS-триггер в любой цифровой схеме, причем вход J будет выполнять роль входа S, а вход K – роль входа R.

Пояснение

. Символы J и K не несут

никакой мнемоники и являются просто

последовательными буквами алфавита.

Получим логическое уравнение JK-триггера. Для этого заполним карту Карно и найдем МДНФ.

|

|

Это и есть логическое уравнение JK-триггера. Его полезно запомнить. Синтезируем базовую схему JK-триггера на основе уже имеющегося RS-триггера, поскольку RS-триггер является простейшей ячейкой хранения одного бита информации. Рассмотрим «черный ящик», на выходе которого стоит RS-триггер:

|

|

Вся будущая структура должна функционировать как JK-триггер. Поскольку на выходе стоит RS-триггер, то именно он определяет выходной сигнал, и, следовательно, обязан переключаться в соответствии с таблицей истинности JK-триггера. Для этого необходимо и достаточно сформировать на его входах S и R нужные сигналы для каждой строки таблицы.

Дополним таблицу истинности JK-триггера двумя столбцами для сигналов S и R и впишем в них нужные комбинации из таблицы возбуждения RS-триггера, чтобы обеспечить каждый переход вида Q(t) -> Q(t+1):

| Q(t) | J | K | Q(t+1) | Нужно подать |

| S | R | |||

| — | ||||

| 1 | — | |||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | — | ||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | — | |

| 1 | 1 | 1 | 1 |

переходы

Эта расширенная таблица позволяет записать СДНФ для сигналов S и R, считая аргументами столбцы Q(t),J,K:

Теперь очевидна реализация JK-триггера:

Рис.2. Принцип

построения

JK-триггера

Следует заметить, что эта структура поясняет лишь принцип построения JK-триггера, в действительности она неработоспособна! Нетрудно догадаться, что при подаче сигналов J = K = 1 такой триггер превратится в автогенератор меандра, поскольку будет непрерывно изменять свое состояние на противоположное.

Поэтому на практике эту схему обычно выполняют двухтактной или вводят дополнительные элементы, превращающие выходную ступень в непрозрачный триггер, устраняя тем самым возможность паразитной автогенерации.

По таблице истинности легко составить таблицу возбуждения JK-триггера:

| Q(t) | J | K | Q(t+1) |

| — | |||

| 1 | — | 1 | |

| 1 | — | 1 | |

| 1 | — | 1 |

JK-триггер принято называть универсальным триггером. Это название отражает тот факт, что на его основе легко построить триггер любого другого типа. Признаком выполнения триггера по двухтактной схеме является наличие двух букв TT в правой части символа изображения триггера. Заметим, что принципиально выполнима задача взаимной трансформации триггеров любых типов.

1.3. Асинхронный Т-триггер (счетный триггер)

Поставим задачу синтезировать схему триггера, который инвертирует свое состояние каждый раз, когда на его единственном управляющем входе T

появляется уровень логической единицы. Наглядно это можно изобразить временной диаграммой, полагая в частном случае, что

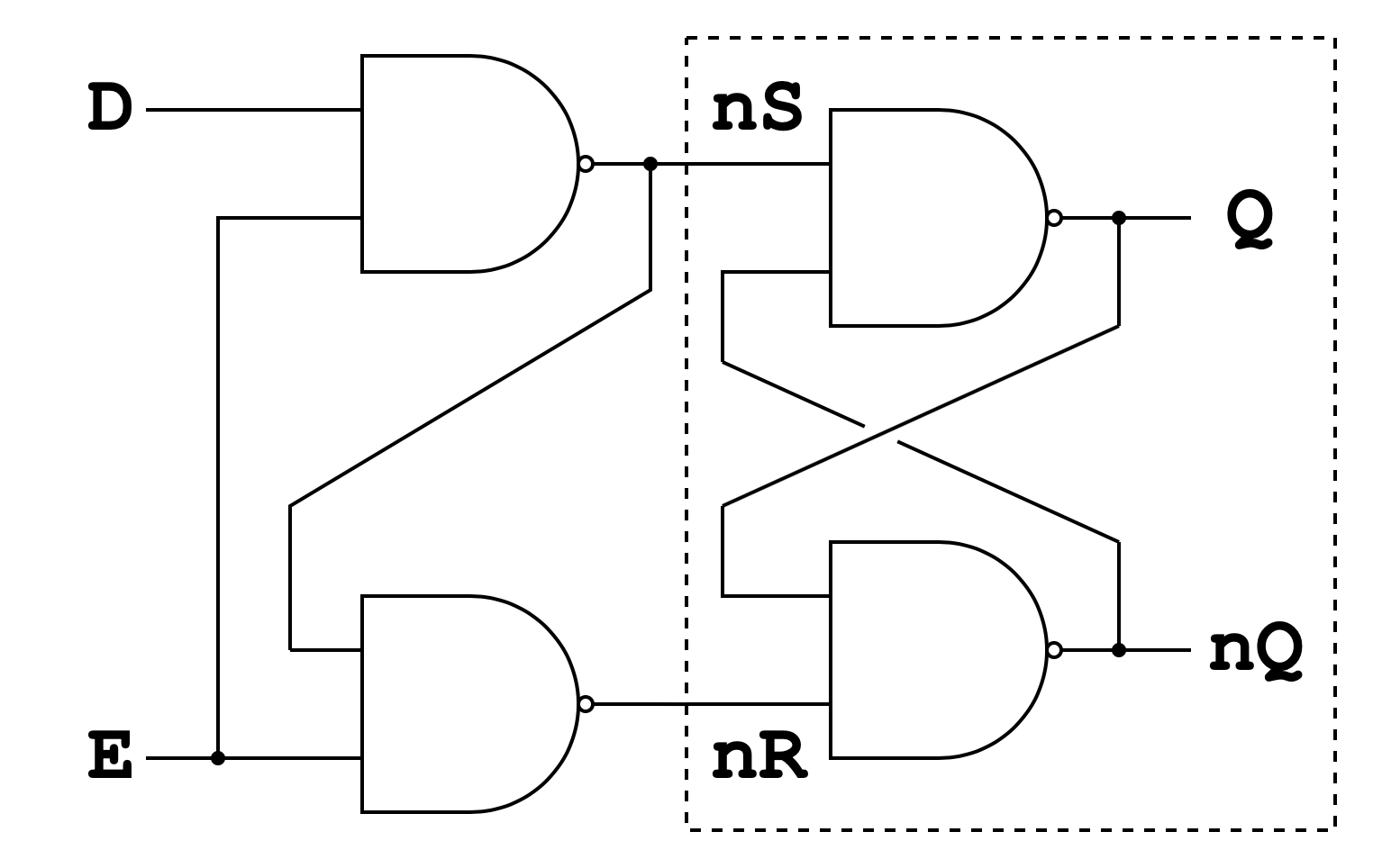

Продвинутый D-триггер

Освоившись с установкой и сбросом внутреннего состояния в простой схеме, перейдем к более интересным вещам. Как и в программировании, теперь мы можем повторно использовать готовые логические блоки, чтобы эффективно абстрагироваться от возрастающей сложности устройств. Это примерно как с кодом — единожды реализовав нужную функцию или алгоритм, ты можешь добавлять их в необходимые места, не заботясь о стеке вызовов и конкретных адресах в памяти.

Как ты помнишь, ключевое неудобство в RS-триггере вызывал тот факт, что при nR = nS = 0 мы получали одинаковое состояние на прямом (Q) и, казалось бы, инверсном (nQ) выходе. Попробуем избавиться от этой проблемы. Для этого будем явно блокировать один из сигналов, если другой в этот момент активен.

Теперь состояние входа данных (D) через пару вентилей NAND подается на оба входа RS-триггера, а сигнал разрешения (E) контролирует момент времени, когда состояние правой половины схемы может меняться.

D-защелка — это почти как D-мейл, только защелка

Можно пойти еще дальше и объединить две защелки в один триггер, который будет срабатывать только по переднему фронту тактового сигнала (переход с низкого уровня в высокий). Это наиболее универсальная схема, так как позволяет мгновенно зафиксировать состояние всех сигналов на входных линиях, а уже потом приступить к формированию результата с помощью комбинационной логики.

Практическое применение

В 4000 серии пару D-триггеров реализует микросхема CD4013 (отечественный аналог — К561ТМ2). Назначение ее выводов ты можешь увидеть на схеме ниже

Обрати внимание, что, помимо входов данных и тактового сигнала, тут выведены контакты для асинхронного сброса и установки внутреннего состояния триггера

Асинхронность означает, что событие происходит мгновенно, не дожидаясь следующего тактового сигнала. И наоборот, обновления с линии данных происходят синхронно с изменениями на линии CLK.

Таким образом, комбинируя микросхемы CD4011 (561ЛА7) и CD4013 (561ТМ2) можно собрать схему с тактовой кнопкой и светодиодом, которая будет помнить свое состояние. Первое нажатие заставит светодиод гореть, второе нажатие его погасит. При этом нам даже не потребуется микроконтроллер и мы не напишем ни строчки кода!

Классификация

RS триггер

Изделия этой категории разделены на две основные группы по принципу сигналов управления. В первой – формируется заданная последовательность выходных сигналов, если установлено состояние «1». После переходе в «0» генерация прекращается. Вторая – способна переключать выходное напряжение соответствующим образом. Как правило, «1» примерно соответствует уровню источника питания.

Также триггеры различают по следующим параметрам:

- синхронность рабочих циклов;

- статические (динамические) способы управления;

- сложность логических схем;

- одно,- или двухступенчатые.

Триггеры на логических элементах и на операционном усилителе

Для реализации статических триггеров хорошо подходит схема усилителя с двумя каскадами. Связь между ними организуют прямую либо с ограничительными резисторами в соответствующих цепях.

Триггер на логических элементах

Триггер (Trigger) Шмитта

Изделия этой категории могут быть созданы с применением разной элементной базы. В данном разделе рассмотрен триггер Шмитта на транзисторах. Он управляется изменением аналогового сигнала. В зависимости от уровня напряжения, выполняется переключение состояния памяти в соответствующее положение «0» или «1».

Триггер Шмидта на транзисторах с подключенной нагрузкой

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Будет интересно Все о законе Ома: простыми словами с примерами для «чайников»

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Физические реализации триггерных систем

В подзаголовке говорится о «триггерных системах» из-за того, что сами по себе эти устройства мало чего стоят. Но если необходимо сделать временную задержку перед выполнением или во время процедуры – их весьма сложно заменить. Также тот факт, что D-триггер может запросто длительное время работать без дополнительной настройки, позволяет его сделать очень ценным элементом любых схем, где необходима временная задержка. Для радиолюбителей они стали настоящим спасением при конструировании автоматических роботизированных станков, ведь эти элементы позволяют сделать временную задержку, необходимую для того, чтобы в рабочую область подать материал или деталь.

RS — триггер

Первым будет рассмотрен RS-триггер. Его условное обозначение приведено на рисунке 1.

S (SET) — вход установки значения 1. R (RESET) — вход сброса (установки значения 0). Входы прямые — активны при подачи логической единицы, неактивны при подаче логического нуля.

Логика работы RS-триггера:

- S=0 R=0 — режим хранения информации (выходы не меняются, Q(t+1)=Q(t) )

- S=1 R=1 — режим записи единицы ( Q(t+1)=1 )

- S=0 R=1 — режим записи нуля ( Q(t+1)=0 )

- S=1 R=1 — запрещенная комбинация (оба входа активны). Значение Q зависит от реализации триггера (не определено в общем случае). Значение перехода из запрещенного состояния Q(t) в Q(t+1) тоже зависит от реализации.

RS — триггер с инверсными входами (рис. 2) работает аналогично, только входы становятся активны при подаче логического нуля, а неактивны при подаче единицы.

Классическая реализация RS-триггера

Классической является реализация RS-триггера на элементах «ИЛИ-НЕ» (рис 3.):

| S | R | Q(t) | Q(t+1) | no Q(t+1) | Описание |

| 1 | режим хранения нуля | ||||

| 1 | 1 | режим хранения единицы | |||

| 1 | 1 | установка в состояние 1 | |||

| 1 | 1 | 1 | режим хранения 1 | ||

| 1 | 1 | режим хранения нуля | |||

| 1 | 1 | 1 | сброс в ноль | ||

| 1 | 1 | запрещено | |||

| 1 | 1 | 1 | запрещено |

Временные диаграммы RS-триггера

Будем считать, что в триггере записано значение «0», попробуем записать «1» (рис. 4).

Если объединить входы R и S триггера, то выход будет определяться тем, какой из элементов сработает раньше («генератор случайных чисел»). Схема и временные диаграммы такого подключения приведены на рисунке 5.

Таблица истинности jk триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, его схема изменена таким образом, что при подаче двух единиц jk триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов он изменяет своё состояние на противоположное. Таблица истинности jk триггера приведена в таблице 1.

Таблица 1. Таблица истинности jk триггера.

| С | K | J | Q(t) | Q(t+1) | Пояснения |

| x | x | Режим хранения информации | |||

| x | x | 1 | 1 | ||

| 1 | Режим хранения информации | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы J=1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим записи нуля K=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | 1 | K=J=1 счетный режим триггера | |

| 1 | 1 | 1 | 1 |

Один из вариантов внутренней схемы JK-триггера приведен на рисунке 1. Он построен по классической двухтактной схеме. Приведенная на рисунке 1 схема удобна для изучения принципов работы данного триггера в счетном режиме.

Рисунок 1. Внутренняя схема jk триггера

Для реализации счетного режима в схеме введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря обратной связи на входах R и S первого триггера никогда не может возникнуть запрещенная комбинация, а то, что она перекрестная, вводит новый режим работы — счетный. При подаче на входы j и k логической единицы одновременно JK-триггер переходит в счетный режим, подобно T триггеру.

Приводить временные диаграммы работы JK-триггера не имеет смысла, так как они совпадают с приведёнными ранее временными диаграммами RS- и . Условно-графическое обозначение приведено на рисунке 2.

Рисунок 2. Условно-графическое обозначение jk триггера

Цифровые микросхемы обычно собираются на элементах «И-НЕ». Тогда схема, приведенная на рисунке 1, преобразуется в схему, показанную на рисунке 3.

Рисунок 3. jk триггер, собранный на логических элементах «И-НЕ»

В промышленно выпускающихся микросхемах обычно кроме входов j и k реализуются входы R и S, которые позволяют устанавливать jk-триггер в заранее определённое исходное состояние. Именно так реализованы микросхемы 155ТВ1, 133ТВ1, SN7472. На рисунке 4 приведена цоколевка этих микросхем.

Двухступенчатый Т-триггер

В двухступенчатом триггере, содержащем два последовательно включённых триггера с обратными связями, «новая» информация запоминается в первом триггере при сохранении «старой» информации во втором. Когда «новая» информация сохранена, и снят активный сигнал с входа Т, происходит стирание «старой» информации и перезапись «новой» информации во второй триггер. Схема двухступенчатого Т-триггера, построенного на двух синхронных RS-триггерах, и временная диаграмма его работы представлены на рис. 5.9.

|

|

а)

б)

Рис. 5.9. Схема (а) и временная диаграмма работы (б) двухступенчатого Т-триггера

Двухступенчатый Т-триггер состоит из двух триггеров – ведущего DD1 и ведомого DD2. Для устранения режима генерации схемы входы синхронизации триггеров включены через инвертор DD3, то есть получается синхронизация инверсными логическими уровнями. Обратные связи с прямого выхода DD2 на вход R DD1 и инверсного выхода DD2 на вход S DD1 создают соответствие сигналов алгоритму работы Т-триггера

Обратите внимание, что сигнал на выходе двухступенчатого Т-триггера появляется после снятия активного сигнала на входе Т, когда происходит перезапись информации из первого триггера во второй. Это обеспечивает нормальную работу (без генерации импульсов) в схеме с обратными связями

Чтобы отличить двухступенчатый триггер от одноступенчатого, на его условном графическом изображении ставится сдвоенная буква (ТТ).

5.6. Двухступенчатый синхронный JK

-триггер

Отличительной особенностью JK

-триггера является то, что он не имеет запрещённых комбинаций входных сигналов на информационных входах. РаботуJK -триггера описывает таблица переходов (таблица 5.5), в которой активным считается сигнал логической 1. Активный сигнал входа J переключает триггер в состояние Q=1, а входа К – в Q=0.

Таблица 5.5

Таблица переходов JK

-триггера

| С | J | K | Qn | Qn+1 |

| — | ||||

| — | ||||

| — | ||||

| — | ||||

| — | ||||

| — | ||||

| — | ||||

| — |

Из таблицы переходов следует, что при одновременной подаче на информационные входы J и K активных сигналов триггер работает как счётный. Такое возможно только в двухступенчатом триггере. Структурная схема JK

-триггера представлена на рис. 5.10.

|

|

Рис. 5.10. Структурная схема JK

-триггера

Как видно из схемы, на входы элементов 3И DD3 или DD4 поступает с выхода триггера DD2 один сигнал логического 0 и один логической единицы. Поэтому на входах J и K могут быть любые сигналы, но на входы S и R DD1 одновременно два активных сигнала поступить не могут.

JK

-триггер является универсальным. На его основе можно создать любую схему триггера. На рис. 5.11 представлена реализация всех ранее рассмотренных триггеров наJK -триггере.

| а) | б) | в) |

Рис. 5.11. Реализация триггеров на основе JK

-триггера:

а – синхронный RS-триггер; б – D-триггер; в – Т-триггер

В серии ТТЛ JK

-триггер выполнен на микросхеме К155ТВ1, в серии КМОП – К561ТВ1 и К176ТВ1, то есть всего по одной микросхеме в серии. Это объясняется малой востребованностью триггеров со статическим управлением для применения в схемах автоматики и телемеханики.

D-триггер

D-триггер (от англ. delay) запоминает входную информацию при поступлении синхроимпульса.

Хранение информации в D-триггерах обеспечивается за счет синхронизации, поэтому все реальные D-триггеры имеют два входа: информационный D и синхронизации С (рис. 12). Под действием синхросигнала С информация, поступающая на вход D, принимается в триггер, но на выходе Q появляется с задержкой на один такт. В D-триггере с динамическим входом прием в триггер информации со входа D происходит в момент смены на входе С уровня 0 на уровень 1.

Рис. 12 — Схема D-триггера

Таблица 3

| C | D | Qt+1 |

|---|---|---|

| 1 | ||

| 1 | 1 | 1 |

Условное графическое обозначение D-триггера показано на рис. 13.

Рис. 13 — Условное графическое обозначение D-триггера

Так как информация на выходе остается неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защелкой. Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рисунке 14.

Рис. 14 — Временная диаграмма D-триггера

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера. Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы «защелкиваются» в этот момент. Отсюда и название — триггер-защелка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера

Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту

Схема такого триггера приведена на рисунке 15, а обозначение на принципиальных схемах на рисунке 16.

Рис. 15 — Схема универсального D-триггера

Рис. 16 — Обозначение универсального D-триггера на принципиальных

схемах

На рис. 17 представлено условное обозначение D-триггера микросхемы К155ТМ2, содержащей два D-триггера. Входы R и S выполняют те же функции, что и в RS-триггере.

Рис. 17 — D-триггер микросхемы К155ТМ2

D-триггер несложно преобразовать в счетный триггер, т. е. такой, состояние которого изменяется после поступления очередного импульса на счетный вход. Для обеспечения счетного режима необходимо вход D соединить с инверсным выходом триггера (рис. 18,а). Из логики работы

D-триггера следует, что после прихода импульса на вход С состояние

триггера будет изменяться на противоположное. Это иллюстрируется

временными диаграммами, или эпюрами напряжений (рис. 18,б). Подобно

таблице истинности, эпюры напряжений дают наглядное представление о работе

устройства.

Рис. 18 — Работа D-триггера в счетном режимеа) — соединение выводов, б) — временные диаграммы

Необходимо отметить, что изменение состояния D-триггера данного типа происходит при изменении напряжения на счетном входе с низкого уровня на высокий. Такое изменение

напряжения часто называют положительным перепадом напряжения или фронтом импульса. Реакцию триггера на положительный перепад напряжения отображают

косой чертой, пересекающей линию входа С (рис. 18,а). Аналогично

изменение напряжения с высокого уровня на низкий называют отрицательным

перепадом напряжения, спадом или срезом импульса. На схемах это отображают

также косой чертой, но повернутой на 90° относительно показанной на

рисунке 18,а. В зависимости от своей внутренней структуры триггер реагирует или

на положительный, или на отрицательный перепад напряжения.

Типы триггеров

В следующих разделах представлены принципы функционирования стандартных устройств. Они могут работать автономно либо в различных комбинациях. Сочетания триггеров в электронике применяют для построения сложных логических схем.

Что такое trigger RS типа

Эти элементы делят на группы по способам управления. Для удобства здесь и далее пояснения сделаны с помощью логических компонентов. При необходимости можно собрать аналогичный триггер на реле или транзисторах.

RS-триггер асинхронный

Работоспособную схему можно собрать из двух типовых элементов «И-НЕ».

Схемотехника, таблица состояний, графики сигналов

RS-триггер синхронный

В этой схеме при подаче «1» на С устройство обеспечивает режим «прозрачности». Изменения на входах R и S с минимальной внутренней задержкой отображаются в промежуточных точках /R и /S. После установки управляющего сигнала «0» включается хранение данных.

Переключение состояний происходит только при наличии управляющего (тактового) сигнала

D-триггер синхронный

На графиках работы видно, что изменение выходного сигнала происходит только при наличии «1» на входе С. Данные сохраняются в неизменном состоянии до поступления следующего импульса синхронизации. В этом цикле обеспечивается беспрепятственная проводимость данных.

Эти устройства имеют отдельный вход для информационных сигналов

D-триггер двухступенчатый

Как и в предыдущем примере, здесь используется один канал поступления данных – D. На схеме показано, как создано более сложное устройство из двух одноступенчатых блоков.

Двухступенчатая «защелка» с управлением синхроимпульсом

T-триггер синхронный

Такие устройства подходят для двукратного уменьшения частоты. На картинке показаны счетчики, собранные на базе триггеров RS и D типа.

Один выходной сигнал формируется на каждые два синхроимпульса

JK-триггер

Рабочие циклы этого устройства аналогичны рассмотренному выше триггеру типа RS. Главное отличие – изменение выходного сигнала на противоположное значение (инверсия) выходного сигнала после подачи «1» на K и J одновременно. Следует подчеркнуть отсутствие запрещенных комбинаций в информационных каналах.

Схема, собранная на элементах «И-НЕ»

Физические реализации триггеров

Базовый элемент создают из полупроводниковых приборов, используя современные технологические процессы для миниатюризации функциональных изделий.

Логический элемент на МОП транзисторах

Триггеры с тиристорами

Для повышения мощности подключаемой нагрузки можно собрать триггер с применением тиристоров. К управляющему электроду присоединяют вход S, к затвору – R. Для поддержания постоянного напряжения на аноде подойдет транзистор, включенный в соответствующую цепь.

Триггеры на релейно-контакторной базе

Несмотря на общие тенденции миниатюризации, вполне допустимо создать функциональный триггер из реле. Подобные решения, в частности, применяют для защиты цепей питания при включении мощных электроприводов.

Синхронные и асинхронные триггеры: в чем разница?

Синхронные устройства имеют только логические (или по-другому – информационные) входы. Асинхронные механизмы срабатывают сразу, как только получили сигнал. Они не ждут, пока пройдёт временная задержка в тех элементах, которые образуют триггер. Асинхронный D-триггер не работает как устройство в обычном понимании. Благодаря этому он имеет один несомненный плюс: всегда, когда подаётся сигнал на вход, этот логический элемент сразу меняет значение выхода, а не ждёт определённой тактовой частоты. Для тех, кто умеет создавать близкие к идеальным схемы, триггеры будут весьма полезны. Синхронные имеют не только информационные входы, у них также есть отдельный вход для подачи тактового сигнала. И именно к ним относится D-триггер. Он состоит из комбинационных схем (КС) и элементов памяти (ЭП). Из-за того что при наличии тактового сигнала вся работа ориентируется на один такт, триггеры и разделили на синхронные и асинхронные устройства. Но конструктивная разница на этом не исчерпывается. Так, именно благодаря тактовому сигналу, его воздействию, можно полностью исключать из внимания переходные процессы, что позволяет, в свою очередь, облегчить работу с электроникой. Именно поэтому синхронный D-триггер является более популярным и используемым на практике. Даже пример, который был приведён в начале статьи, подразумевал его использование.

Схемы запуска триггера

Как говорилось выше для переключения триггера из одного устойчивого состояния в другое необходимо подать на его входы управляющий (запускающий) импульс. В зависимости от того как подавать управляющий импульс существует несколько видов схем запуска триггера:

- 1.В зависимости от способа управления:

- — раздельный способ;

- — счётный (общий) способ.

- 2.В зависимости от места поступления импульса запуска:

- — базовый;

- — коллекторный.

Для запуска триггеров используют короткие импульсы, которые формируются дифференциальными RC- или RL- цепочками. Так как при прохождении импульса через дифференциальную цепочку формируется два разно полярных импульса, то для предотвращения двойного срабатывания триггера между дифференциальной цепочкой и точкой входа запускающего импульса ставят диод, который отсекает второй импульс. В общем случае схема запуска имеет следующий вид:

Схема запуска триггера.

Рассмотрим схему раздельного запуска триггера с подачей управляющих импульсов в базовые цепи транзисторов.

Симметричный триггер с независимым смещением и раздельным запуском.

В данной схеме импульс, поданный на один из входов триггера, переключает его из одного устойчивого состояния в другое. Если импульс подать на другой вход, то состояние триггера изменится на противоположное. Схема запуска состоит из резисторов Rз1 и Rз2, конденсаторов Сз1 и Сз2, диодов VD1 и VD2. Остальные элементы являются цепями питания и смещения транзисторов VT1 и VT2.

Симметричный триггер с раздельным запуском называется RS-триггером, он имеет два входа и два выхода. Входы, на которые подают управляющие импульсы, называются установочными и обозначают R и S, выходы триггера обозначают Q и –Q.

Рассмотрим схему со счётным (общим) запуском триггера и подачей управляющих импульсов в базовые цепи транзисторов.

Симметричный триггер с независимым смещением и счётным запуском.

В данном случае импульсы подаются на общий вход триггера, и каждый импульс приводит к изменению устойчивого состояния триггера. При рассмотрении работы данного типа триггера может возникнуть ощущение, что произойдёт двойное срабатывание, однако за счёт того что у открытого транзистора потенциал базы выше, чем у открытого, то один из диодов сработает раньше другого, а у открытого транзистора диод будет заперт высоким напряжением базы.

Симметричный триггер с общим запуском называется T-триггером и частота переключения данного типа триггера вдвое меньше, чем частота поступающих импульсов запуска.

На процесс перехода триггера из одного состояния в другое существенное значение оказывает время длительности управляющего импульса, например, если импульс имеет недостаточную длительность, то один из транзисторов триггера может не открыться и триггер не сработает.

Значение слова триггер

(англ. trigger), спусковое устройство ( спусковая схема ), которое может сколь угодно долго находиться в одном из двух (реже многих) состояний устойчивого равновесия и скачкообразно переключаться из одного состояния в другое под действием внешнего сигнала. Т. имеет два выхода: основной и инверсный. Каждому состоянию Т. соответствуют определённые сигналы на его выходах, отличающиеся своим уровнем. В одном состоянии на основном выходе Т. формируется сигнал высокого уровня, а на инверсном ≈ низкого; в др. состоянии, наоборот, сигналы высокого и низкого уровней формируются соответственно на инверсном и основном выходах. Т. характеризуется следующими важнейшими параметрами: быстродействием, временем срабатывания, уровнями входных и выходных сигналов. Быстродействие Т. определяется как максимальное возможное число переключений в единицу времени. Время срабатывания определяется временем перехода Т. из одного состояния в другое и характеризует задержку выходного сигнала Т. относительно входного. Под уровнем входного сигнала понимают минимальное значение сигнала, необходимое для переключения Т. Уровень выходного сигнала у большинства Т. не ниже уровня входного сигнала, чем обеспечивается возможность их последовательного соединения без промежуточного усиления.

Наибольшее распространение получили электронные Т., выполненные на электронных лампах, газоразрядных приборах, полупроводниковых диодах, транзисторах разных типов и особенно на интегральных микросхемах; иногда применяются также Т. на магнитных элементах, элементах пневмо- и гидроавтоматики и др. По характеру входных сигналов различают Т. с потенциальными входами (прямым и инверсным) и динамическими входами (также прямым и инверсным). Т. с потенциальными входами реагируют на сигнал высокого уровня на прямом входе и низкого уровня на инверсном входе. Т. с динамическими входами реагируют на перепады (изменения уровня) входных сигналов: положительный на прямом входе и отрицательный на инверсном.

══Наиболее часто применяют: Т. со счётным входом (Т-триггер), который изменяет своё состояние на противоположное с каждым входным сигналом; Т. с двумя установочными входами (R ≈ S-триггер), изменяющий своё состояние только при воздействии управляющего сигнала на определённый вход (R-или S-вход), причём повторное воздействие сигнала на тот же вход Т. не изменяет его состояния; универсальный Т. (J ≈ K-триггер), обладающий свойствами Т-триггера и R ≈ S-триггера; Т. задержки (D-триггер), состояние которого и соответствующий ему выходной сигнал повторяют входной сигнал. Кроме Т. этих типов, применяют комбинированные Т., представляющие собой универсальные многофункциональные устройства с большим числом входов.

Указанные выше Т. относят к симметричным; применяют также несимметричные Т. (Т. Шмитта). Несимметричный Т. переходит из одного состояния в другое по достижении входным сигналом одного уровня (порога срабатывания), а в исходное состояние возвращается при уменьшении входного сигнала до некоторого др. уровня. Существуют и многостабильные Т., обладающие числом устойчивых состояний, большим, чем два.

Т. различных типов применяют в устройствах цифровой вычислительной техники и автоматики. С использованием Т. строятся цифровые автоматы с программным управлением для дискретной обработки информации (в частности, счётчики, пересчётные устройства, регистры разных типов, дешифраторы, сумматоры и др.), формирователи импульсов, цифровые делители частоты и т.д. В цифровой автоматике Т. выполняют функции элементарных автоматов с памятью, имеющих 2 состояния, которым соответствуют два возможных значения двоичной логической переменной (х = 0 и х = 1). Такие Т. подразделяются на асинхронные и синхронные. Синхронные (тактируемые) Т. выполняют свои функции только при воздействии на их входы периодических тактовых сигналов (обычно меандрового типа), синхронизирующих работу Т. Синхронные Т. подразделяются на однотактные и двухтактные. Последние представляют собой систему из двух Т., выполняющих одну и ту же логическую операцию, но со сдвигом во времени на длительность полутакта входного тактового сигнала. Удвоение действий Т. необходимо для разделения во времени приёма информации, доставляемой входными сигналами, и передачи информации с выходов Т. на др. элементы устройства (или на его вход).

Лит.: Ицхоки Я. С., Овчинников Н. И., Импульсные и цифровые устройства, М., 1972; Старостин А. Н., Импульсная техника, М., 1973; Каган Б. М., Каневский М. М., Цифровые вычислительные машины и системы, М., 1973.

Ю. Б. Барабанов, И. А. Данильченко,

Е. И. Петровичев.